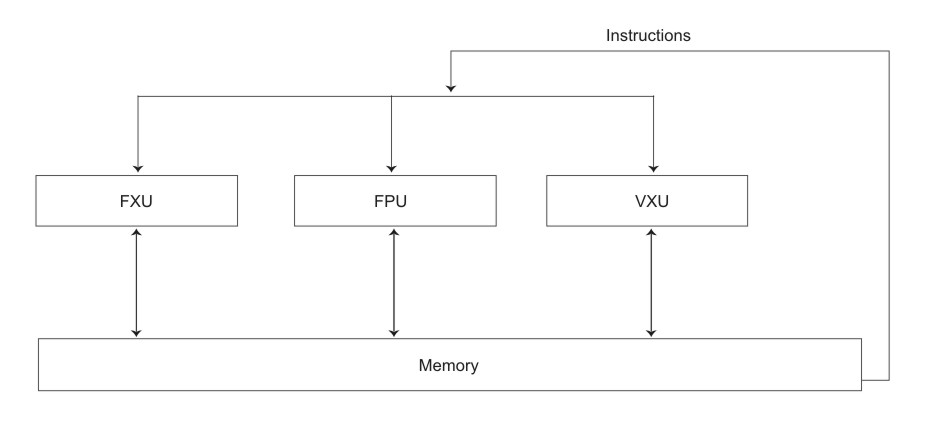

The 128-bit Vector/SIMD Multimedia Extension unit (VXU) operates concurrently with the PPU’s fixed-point integer unit (FXU) and floating-point execution unit (FPU).

Like PowerPC instructions, the Vector/SIMD Multimedia Extension instructions

are 4 bytes long and word-aligned. The Vector/SIMD Multimedia Extension instructions

support simultaneous execution on multiple elements that make up the 128-bit

vector operands. These vector elements may be byte, halfword, or word.

The Vector/SIMD Multimedia Extension instructions are fully described in the PowerPC Microprocessor Family, Vector/SIMD Multimedia Extension Technology Programming Environments manual.

All Vector/SIMD Multimedia Extension instructions are designed to be easily "pipelined".

Parallel execution with the PPE’s integer and floating-point instructions

is simplified by the fact that Vector/SIMD Multimedia Extension instructions:

- do not generate exceptions (other than data-storage interrupt exceptions on loads and stores),

- do not support unaligned memory accesses or complex functions, and

- share few resources or communication paths with the other PPE execution units.